# Proceedings of the 2006 Workshop on Embedded Systems Education

## **Editor**

Dr. Jeff Jackson

The University of Alabama

October 26, 2006 Seoul, South Korea

**ARTIST2**

## **Proceedings**

## 2006 Workshop on Embedded Systems Education

**WESE2006**

**Editor**

**Jeff Jackson**

Seoul, South Korea

October 26, 2006

## Organizer's Message

I am pleased to present this second workshop on embedded system education associated with the 2006 EMSOFT embedded software conference.

The workshop consists of multiple sessions focusing on embedded systems education programs and consortia; embedded systems courses and curricula issues; embedded systems hardware and methodologies; and embedded systems curricula, programs and projects. I expect the sessions to give matter to lively, animated and enriching discussions as they did at the first workshop held last year.

The organizing and program committees and additional reviewers selected sixteen papers for inclusion in this workshop from international academic and industrial authors. I would like to thank the organizing committee and the program committee members for their time and efforts in inviting papers, organizing reviewers, and for providing general assistance to the workshop organization. Without their efforts the workshop would not have been possible. I would like to thank the authors for their manuscript submissions and their timely response to implement improvements suggested by the reviewers. Finally, I would like to thank IEEE, ACM and ARTIST2 organizations for their support.

As last year, I feel this first workshop is a great success. However, there exist many opportunities for international cooperation in the community of embedded systems researchers and educators and I look forward to those efforts.

Jeff Jackson

## **Organizing Committee Members**

Jeff Jackson, The University of Alabama, USA

Paul Caspi, Verimag-CNRS, France

Jogesh Muppala, The Hong Kong University of Science and Technology, Hong Kong

Wayne Wolf, Princeton University, USA

John K. Zao, National Chiao Tung University, Taiwan

## **Program Committee Members**

Tom Conte, North Carolina State University, USA Mats Daniels, Uppsala University, Sweden Jen Davoren, The University of Melbourne, Australia Kenji Hisazumi, Kyushu University, Japan Jin Hyung Kim, KAIST, South Korea Yann-Hang Lee, Arizona State University, USA Kenneth G. Ricks, The University of Alabama, USA Chi-Sheng (Daniel) Shih, National Taiwan University

## 2006 Workshop on Embedded Systems Education

October 26<sup>th</sup>, 2006, Seoul, South Korea

## **Program**

## **8:30 Opening**

## 8:45 Education Programs and Embedded Systems Consortia

- Stylianos Mamagkakis: Research Network for System Level Design of Embedded Systems: Dynamic Memory Allocation Design Flow Case Study

- Kenji Hisazumi: QUBE: A Practical Education Program for System LSI Designers

- Tai-Yi Huang: The Embedded Software Consortium of Taiwan A Progress Report of Educational Activities

## 10:00 Coffee Break

## 10:20 Embedded Systems Courses and Curricula Issues

- Tulika Mitra: Challenges in Designing Embedded Systems Courses

- **Kenneth Ricks**: Addressing Embedded Programming Needs within an ECE Curriculum

- **Jogesh K. Muppala**: Bringing Embedded Software Closer to Computer Science Students

- Shiao-Li Tsao: The Development and Deployment of Embedded Software Curricula in Taiwan

## 12:00 Lunch

## 13:20 Embedded Systems Hardware and Methodologies

- Shekhar Sharad: Methodologies to Bring Embedded Systems to Non-EE Students

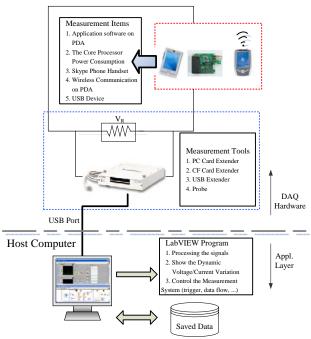

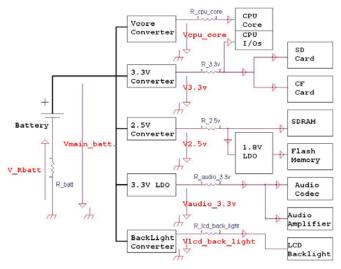

- Shanq-Jang Ruan: Development and Analysis of Power Behavior for Embedded System Laboratory

- Chi-Sheng Shih: Toward HW/SW Integration: Networked Embedded System Design

• Falk Salewski: Hardware Platform Design Decisions in Embedded Systems - A Systematic Teaching Approach

## 15:00 Coffee Break

## 15:20 Embedded Systems Curricula, Programs and Projects

- M. Balakrishnan: Experiences of a Summer Workshop in Embedded Systems

- Hans-Gerhard Gross: The Delft MS Curriculum on Embedded Systems

- **Niklas Adamsson**: Experiences from large embedded systems development projects in education, involving industry and research

- Lindsay T. Kane: The Windows Embedded Academic Program Retrospective & Directions, 2002-2006

- Masaki Yamamoto: An Extension Course for Training Trainers of Embedded Software

## 17:30 Conclusions and Future Considerations

## **Table of Contents**

| Organizers' Message                                                          |

|------------------------------------------------------------------------------|

| Programiv                                                                    |

| Research Network for System Level Design of Embedded Systems: Dynamic Memory |

| QUBE: A Practical Education Program for System LSI Designers                 |

| The Embedded Software Consortium of Taiwan - A Progress Report of            |

| Challenges in Designing Embedded Systems Courses                             |

| Addressing Embedded Programming Needs within an ECE Curriculum               |

| Bringing Embedded Software Closer to Computer Science Students               |

| The Development and Deployment of Embedded Software Curricula in Taiwan      |

| Methodologies to Bring Embedded Systems to Non-EE Students                   |

| Development and Analysis of Power Behavior for Embedded System Laboratory    |

| Toward HW/SW Integration: Networked Embedded System Design                   |

| Hardware Platform Design Decisions in Embedded Systems - A Systematic                                                                 | 59     |

|---------------------------------------------------------------------------------------------------------------------------------------|--------|

| Teaching Approach                                                                                                                     |        |

| Falk Salewski, and Stefan Kowalewski, Aachen University                                                                               |        |

| Experiences of a Summer Workshop in Embedded Systems                                                                                  | 67     |

| Kolin Paul and M. Balakrishnan, Indian Institute of Technology Delhi                                                                  |        |

| The Delft MS Curriculum on Embedded Systems                                                                                           | 73     |

| Hans-Gerhard Gross and Arjan van Gemund, Delft University of Technology                                                               |        |

| Experiences from large embedded systems development projects in education,                                                            | 81     |

| involving industry and research  Martin Törngren, Martin Grimheden, and Niklas Adamsson, Royal Institute of Tech                      | mology |

|                                                                                                                                       |        |

| The Windows Embedded Academic Program – Retrospective & Directions, 2002-2006<br>Lindsay T. Kane and D. Stewart W. Tansley, Microsoft | 89     |

| An Extension Course for Training Trainers of Embedded Software                                                                        | 95     |

| Masaki Yamamoto, Shinya Honda, Hiroaki Takada, Kiyoshi Agusa, Hiroyuki Tomiy                                                          | rama,  |

| Kenji Mase, Nobuo Kawaguchi, and Nobuyuki Kaneko,Nagoya University                                                                    |        |

## Research Network for System Level Design of Embedded Systems: Dynamic Memory Allocation Design Flow Case Study

Stylianos Mamagkakis<sup>1, 3</sup>, David Atienza<sup>2</sup>, Francky Catthoor<sup>3</sup>, Dimitrios Soudris<sup>1</sup> and Jose M. Mendias<sup>2</sup>

<sup>1</sup> VLSI Design Center-Democritus Univ. of Thrace 67100 Xanthi, Greece {smamagka,dsoudris} @ee.duth.gr

<sup>2</sup> DACYA, Univ. Complutense de Madrid 28040 Madrid, Spain {datienza,mendias} @dacya.ucm.es <sup>3</sup> Interuniversity Micro-Electronics Centre (IMEC vzw) 3001 Heverlee, Belgium {mamagka,catthoor} @imec.be

#### **Abstract**

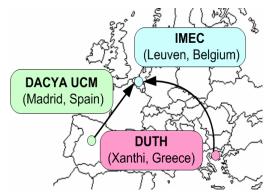

The challenges encountered in system level design require a global approach and considerable manpower, which are not likely to be found in a single organization. Cooperation and sophisticated communication between partners from both academia and industry are required. This paper describes the formal relationship and collaboration between IMEC and several Universities for research and training in the domain of system level design in embedded systems. IMEC (Leuven, Belgium) provides a meeting point between multiple academic institutions and a gateway to relevant information and drivers from the industry, unifying the common research goals of several academic groups working in this area in a consistent flow, sensitive to the market needs. In this paper we focus in the general concept of the cooperation network, which can be illustrated shortly by one part of it, namely the dynamic memory allocation issues of the design flow and the related universities in this effort: DUTH (Xanthi, Greece) and DACYA UCM (Madrid, Spain).

## 1. Introduction

The collaboration illustrated in this paper addresses the needs for a unified, consistent global approach to the various problems encountered in embedded system design. These problems are so closely interconnected that it is common to worsen one aspect of the embedded system design, while trying to improve another [1]. In fact, a small research group with limited resources will ignore the global view in order to maximize its potential within its limited research focus. In order to realize a global approach, without sacrificing quality, a network of research groups is needed. It should be guided by a coordinator that has sufficient critical mass and has access to the necessary information to work on practically relevant end goals.

IMEC with its unique balance between academic and industrial R&D can lead this effort of a star-shaped training and research network. Its geographical location in Belgium offers a unique meeting point for researchers of universities all across Europe, where they can be trained and establish a collaboration towards interconnected goals in embedded system design. The context of the collaboration focuses mostly on the mapping of concurrent, dynamic applications, which are increasingly important in multimedia and network applications. Several design steps are required to cost-effectively map the data and tasks in such applications to a multi-processor platform.

## 2. Dynamic Memory Allocation Design Flow Case Study

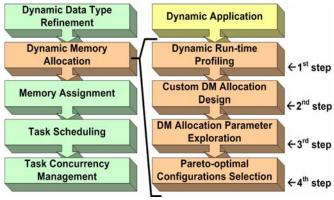

Modern embedded applications have become increasingly dynamic and consist of multiple tasks, which run in multi-processor embedded systems. Design optimizations at the system level are required to optimize the energy consumption, memory footprint, memory accesses and execution time of the final design [1]. A complete optimization design framework is proposed by IMEC in collaboration with its university partners at the system level (see Figure 1), which can be followed in a step-by-step procedure. Each stage consists of systematic design methodologies (or steps), which are closely interconnected and the outputs of the higher ones pass their constraints to the lower ones (more details about the optimization steps and the way they are derived can be found in [2]).

These systematic methodologies require many person-years of research to be developed and perfected and different research networks are assembled in order to take advantage of the expertise of the individual researchers that comprise them. In fact, the proposed system level methodology comprises the combined effort of 14 PhD students and 7 professors from IMEC, the Democritus

University of Thrace (DUTH located in Xanthi, Greece) and the Department Arquitectura de Computadores y Automatica (DACYA UCM located in Madrid, Spain), as shown in Figure 2. Earlier on, also ESAT (K.U. Leuven, Belgium) and recently also U. Bologna have become evolved (see Sect. 4).

Fig.1. System level design optimization steps and dynamic memory allocation sub-steps

As shown in Fig. 1, the transformation and refinement of the original dynamic data types in the specification are addressed. The transformation and refinement of the original dynamic data types in the specification are addressed. IMEC focuses its efforts both on dynamic multimedia applications, e.g. scalable video coding, dynamic image processing, video games, graphical user interface with animation of rendered multimedia objects, as on wireless network applications. In both cases, the target is to embed them on a cost/power-sensitive platform. In these applications, the conventional compile-time techniques only allow to come up with static solutions that assume worstcase and hence much too pessimistic requirements on memory footprint and performance. Hence, the data type transformation methodology was further developed and extended to generate a low cost implementation in terms of performance, memory footprint and energy consumption, which is especially suited for portable appliances, involving dynamic data types. Trade-offs up to several orders of magnitude have been obtained for realistic applications. Also an effective prototype tool has been completed to automatically profile the evolving dynamic memory behavior of the application and adding a systematic exploration technique was started. This research has happened in cooperation with the Univ. Compl. of Madrid and Democr. Univ. Thrace. It builds further on the past experience in the Matisse research project for wired telecom protocols.

The refined dynamic data types still have to be (de)allocated in the virtual memory space and this typically happens with a dynamic memory manager. The dynamic memory manager is analyzed separately on the right side of

Fig. 1. In this case, standard library based solutions lead to much access and footprint overhead compared to the minimal achievable costs. Hence, we have further extended our techniques to fully automatically explore cost-efficient custom dynamic-memory manager solutions exploring still the complete search space in a systematic way, including now also the total energy consumption as an overall objective on top of the ones for memory accesses and footprint. All this is based on a detailed analysis of the (de)allocated patterns of the application. Compared with conventional (dynamic) memory management techniques for embedded systems, IMEC has obtained significant gains, both for multi-media applications and for wireless networks. A tool has been developed that supports the complete trajectory, starting from C++ source code.

The performance and energy consumption of the shared memory hierarchy on a platform depends largely on how the data access of a dynamic application is ordered and assigned to the physically available memories. Therefore, IMEC has developed new techniques to solve the data-tomemory assignment problem for multi-tasked applications where data of dynamically created/deleted tasks is allocated at runtime. In contrast to the previous years where focus was mainly on memory access scheduling and assignment, work now started on a complete script for task-level data transfer and storage exploration. For this purpose a representative application and target platform were selected, and the different steps were evaluated that are required to bridge the gap between the high-level object-oriented specification of data in dynamic concurrent types, together with their realization on a distributed hierarchical memory organization. We are also investigating the use of a hardware emulation platform to evaluate the mappings. This research was executed in cooperation with the Univ. Complutense Madrid, Univ. of Bologna, and Univ. Barcelona.

To show the productivity of such combined approach, just in the dynamic memory allocation step, the cooperative work of 3 to 4 PhD candidates from each research group working full-time during the last 3 years for the development of the dynamic memory allocation methodologies have accomplished the development of 4 national and European funded research projects and the publication of 4 internal technical reports, 21 conference papers, 4 journal papers and 1 book chapter.

## 3. IMEC – Universities Network

The network between the research groups in IMEC and in the universities was star-shaped up to now. This means that the formal relationship is between any given university and IMEC and not yet between the universities themselves. The typical research work plan involves regular visits of at least one researcher of each group to IMEC for a period of 3 to 6 months per year. Researchers working in the

same optimization step have to overlap for at least 3 months each year to synchronize with each other properly.

Fig. 2. IMEC-Universities network for embedded system design

In the case of the research and training required for the optimization step of dynamic memory allocation, one PhD candidate from DUTH and one from DACYA UCM have spent 20 and 21 months respectively in IMEC in the last 3 years. The economic support for the travel and cost of living abroad at this stage is largely provided by EU-funded Marie Curie Fellowships [4].

The EU-funded Marie Curie Fellowships are not tied to other specific projects (e.g., IST or national projects) but are a project on itself. The money that the PhD candidates receive are on addition to their existing funds and are provided in order to pay for their travel costs, their accommodation and living expenses in the country where their host institution is (i.e., in this case IMEC, Leuven).

During their stay in IMEC, the researchers (mainly PhD students) follow general training courses (e.g. "Speaking in public" and "Writing technical reports") and more specialized courses on the unified meta-design flow concepts [1], which are a basis for the global approach of system design. Additionally, they follow specialized courses on the latest system design flows, design toolkits and improvement methodologies.

Finally, they enjoy a high quality research environment (both in facilities and research personnel) and are given the attractive opportunity to interact with both the industrial and the academic international world. Also, this includes seminars once every week from prominent industry and academic figures in the IMEC auditorium.

During each visit, the researchers from the universities collaborate also with the corresponding researchers in IMEC (which work on dynamic memory allocation in this particular case study) and define the interactions between the steps with researchers working in other optimization steps. Most importantly, in each visit in IMEC they kick start the research of one systematic methodology (step) of the dynamic memory allocation and then they continue their research on this step, when they

return in their research group back in their university. For the rest of the year, they retain their strong cooperation by email, web conferencing and phone-conference calls.

The PhD candidates also coordinate the effort within their research groups devoted to the same research goal. The research done locally in each university is supported by funds from the corresponding laboratory acquired through associated research projects or research grants. These research projects are not directly related to the Marie-Curie fellowships but are related to the type of research that is done during the fellowships in the host institution (e.g. see AMDREL project [5]).

## 4. Conclusions and Future Prospects

The research network addressed in this paper, has been very successful in the field of dynamic memory allocation and system level design for embedded systems and already 2 students (i.e. M. Leeman and D. Atienza) have received their PhDs, while working in the network environment. This collaboration is and will be continued and extended in the future to other research topics. Finally, a polyhedron-shaped network between the current groups and additional excellent institutions in Europe, like DEIS University of Bologna and CS 12 of Dortmund, is under construction to ensure the best interaction and mobility between the partners. Further actions under the ARTIST2 [6] and HIPEAC [7] umbrella are also envisioned.

## Acknowledgements

This work is partially supported by the E.C. funded program AMDREL IST-2001-34379, the Spanish Government Research Grant TIN2005-05619 and E.C. Marie Curie Fellowship contract HPMT-CT-2000-00031.

## **REFERENCES**

- [1] F. Catthoor et al., "Unified meta-flow summary for low-power data-dominated applications", Kluwer Publications, 2000.

- [2] IMEC Design Technology Program, <a href="http://www.imec.be/ovinter/static\_research/designtechnology.shtml">http://www.imec.be/ovinter/static\_research/designtechnology.shtml</a>

- [3] S. Mamagkakis et al., "Energy-efficient dynamic memory allocators at the middleware level of embedded systems", in Proc. of EMSOFT, S. Korea, 2006

- [4] Marie Curie Actions Human Resources and Mobility Activity, http://europa.eu.int/comm/research/fp6/mariecurieactions/action/fellow\_en.html

- [5] AMDREL project "Architectures and Methodologies for Dynamic REconfigurable Logic", http://vlsi.ee.duth.gr/amdrel/

- [6] ARTIST 2, Network of Excellence on embedded system design, http://www.artist-embedded.org/artist/

- [7] European Network of Excellence on High-Performance Embedded Architecture and Compilation, http://www.hipeac.net/

## QUBE: A Practical Education Program for System LSI Designers

Akira Tsukizoe System LSI Research Center, Kyushu University 305-3-8-33 Momochihama, Sawara-ku, Fukuoka 814-0001 JAPAN +81-92-847-5190

tsukizoe@slrc.kyushu-u.ac.jp

Kenji Hisazumi System LSI Research Center, Kyushu University 305-3-8-33 Momochihama, Sawara-ku, Fukuoka 814-0001 **JAPAN** +81-92-847-5190

nel@slrc.kyushu-u.ac.jp

Takanori Hayashida System LSI Research Center, Kyushu University 305-3-8-33 Momochihama, Sawara-ku, Fukuoka 814-0001 **JAPAN** +81-92-847-5190

hayasida@slrc.kyushu-u.ac.jp

Hiroto Yasuura System LSI Research Center, Kyushu University 305-3-8-33 Momochihama. Sawara-ku, Fukuoka 814-0001 **JAPAN** +81-92-847-5190

yasuura@slrc.kyushu-u.ac.jp

Akira Fukuda The Department of Computer Science and Communication Engineering, Kyushu University 744 Motooka Nishi-ku, Fukuoka 819-0395, JAPAN +81-92-802-3644

fukuda@f.csce.kyushu-u.ac.jp

## Tsuneo Nakanishi

The Department of Computer Science and Communication Engineering, Kyushu University 744 Motooka Nishi-ku, Fukuoka 819-0395, JAPAN +81-92-802-3644 tun@f.csce.kyushu-u.ac.jp

## **ABSTRACT**

The System LSI Research Center (SLRC), Kyushu University, has launched a project educating System LSI designers referred to as QUBE since 2005. The intended applicants for the QUBE are senior engineers who are required to have wide knowledge and practical skills on hardware, embedded software, and system design. QUBE made a curriculum that students can learn advanced hot topics in each technical region and exercise to design and implement System LSI which consists of hardware and embedded software. QUBE originally developed an exercise centric course material for latter program in the curriculum. QUBE provides 16 classes (35 days) in 18 weeks according to the plan in 2005 school year. 106 applicants ware submitted to classes. 89% students ware satisfied with QUBE classes according to questionnaire.

## **Keywords**

Education, SoC, System LSI, Architect, Co-Design

## 1. INTRODUCTION

The importance of System LSI is increasing. System LSI are embedded to various products such as cellar phones, TV, etc. It is, however, difficult to design appropriately System LSI considering aspects of hardware, software, and also business. It requires wide knowledge and know-how of technology in such multiple areas for engineers to design and develop System LSI. In Japan, universities provide classes in which professors lecture individual technologies only. The class integrating various technologies to learn designing System LSI was not provided. There is no other education organization to educate engineers required to develop

System LSI. Industry under heavy cost competition cannot use budgets for educating engineers.

The System LSI Research Center (SLRC), Kyushu University, has launched a project educating System LSI designers referred to as QUBE since 2005. The intended applicants for the QUBE are senior engineers who are required to have wide knowledge and practical skills on both hardware and embedded software design. The QUBE also intends researchers who want to know technologies used in the field as its target.

This paper is organized as follows: Section 2 introduces the QUBE project and Section 3 describes related works and QUBE properties. Section 4 describes its missions and Section 5 shows the curriculum of the OUBE. Section 6 explains newly developed course referred to as System LSI Design Training Course. Section 7 reports the activities of the QUBE in 2005. Finally, section 8 concludes this paper.

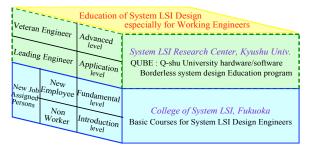

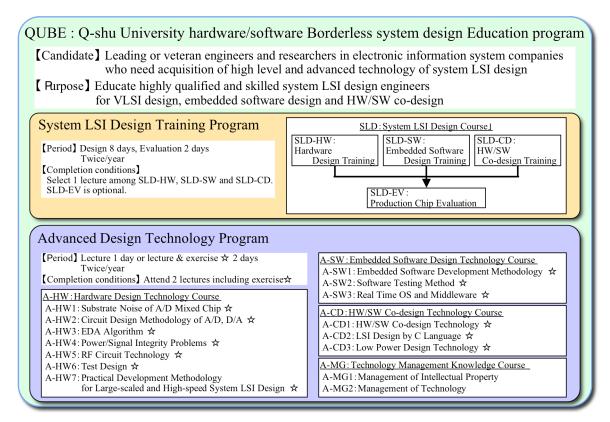

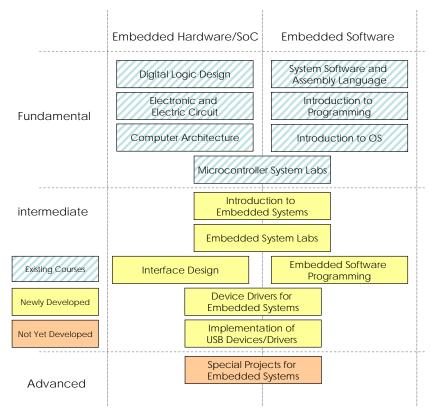

Figure 1 The consistent curriculum of the QUBE and College of System LSI, Fukuoka

Figure 2 The Curriculum run in 2005

## 2. PROJECT OVERVIEW

This section explains the QUBE project overview.

The QUBE has begun as a one of a unit in System LSI Research Center, Kyushu University funded by Ministry of Education, Culture, Sports, Science and Technology, Japan. The QUBE is a five year project from July, 2005 to March, 2010. The QUBE is administered by the QUBE project members consisted of four full-time staffs and three concurrent staffs. The QUBE has a advisory committee, which consists of the QUBE project members, professors invited from Kyushu University, other universities, and industries for the QUBE classes, and members Teaching Staff Meeting of College of System LSI, Fukuoka[1].

Before QUBE, Prof. Yasuura who is a leader of the QUBE began College of System LSI, Fukuoka for educating entry-level hardware designer since 2001[1]. The QUBE has begun to provide advanced-level education for System LSI designers, hardware engineers, and embedded software engineers. To educate those engineers from entry-level to advanced level QUBE cooperates with College of System LSI, Fukuoka and make a consistent curriculum as shown in Figure 1. College of System LSI, Fukuoka provides entry and basic level classes and QUBE provides advanced-level classes.

## 3. RELATED WORKS

This section introduces some related works that educates SoC design, LSI design and embedded software. There are many education courses to educate these topics in the world. The SoC Consortium of Taiwan[2] is developing curriculum and course

materials to educate LSI design and embedded software for master course students. NEXCESS[3] is developing them to educate embedded software for industrial engineers.

The specialty of the QUBE is that the targets of the QUBE are industrial engineers. Most targets of education courses like SoC consortium of Taiwan are students who belong to universities. It is required to design QUBE courses especially for industrial engineers. For example, each lecture for them should keep short since they are too busy to take long lecture. One of merits to set a target to industrial engineers is that the QUBE can obtain industrial needs directly. In feature, curriculum and course materials developed by the QUBE according to industrial needs will be used as one for educating master course and/or undergraduate students.

The next specialty is that QUBE has a integrated curriculum including hardware design, embedded software, hardware / software co-design, and also managements skills for engineers who develop System LSI.

## 4. MISSIONS

The mission of QUBE is to educate System LSI designers who can design value added System LSI considering with both of hardware and embedded software. System LSI designers consists of hardware engineers, embedded software engineers, and hardware / software co-design architects. The targets of our program is senior engineers who would like to learn advanced technical topics. These engineers are basically employed by electrical and/or information related industry.

The goal of QUBE is to educate 180 engineers after 3 years, 360 engineers after 5 years who have skill levels as follows:

## a) Hardware Engineers:

Hardware engineers are not only able to design a part of hardware of the System LSI, but they also can understand requirement specifications and solve problems related with hardware / software interfaces.

#### b) Embedded Software Engineers:

Embedded Software Engineers are not only able to design and implement a part of software of the System LSI, but they also can understand requirement specification and solve problems related with hardware / software interfaces.

#### c) Hardware / Software Co-Design Architects:

Hardware / Software Co-Design Architects can design System LSI and write requirement specifications both of hardware and embedded software appropriately. Architects can understand tradeoffs between hardware and embedded software implementation and design System LSI considering with these tradeoffs.

QUBE provides practical exercise centric classes to educate these engineers and architects as follows: a) QUBE invites top professors those who research and develop something related to hot topics. b) QUBE develops exercise centric classes in which students can use EDA tools and development environments employed at fields in industries. QUBE employs tools provided by VDEC (VLSI Design and Education Center, Tokyo University) [4] and design and verification lab serviced by Industry Science Technology Foundation, Fukuoka to compress costs using these tools[5].

## 5. CURRICULUM

In this section, we describe the curriculum of QUBE project. QUBE curriculum aims at educating three technical domain of System LSI; hardware engineer, embedded software engineer, and hardware / software co-design architect as mentioned in previous section. The curriculum run in 2005 is shown as Figure 2.

The curriculum consists of two parts as follows:

## (1) System LSI Designer Training Program

System LSI Designer Training Program aims at educating engineers who can design systems considering both aspects of hardware and embedded software. This program consists of two classes: a) System LSI Design Training and b) Trial Chip Evaluation Lab. b) will be run in 2006.

System LSI Design Training class aims at educating all of hardware design, embedded software design and implementations, and co-design. This class also aims that students can be learned practical design and implementation skills through exercise. In this exercise, students implement something using hardware and embedded software on the processor embedded FPGA board.

In this class, students form some teams and each team implement a system. A team member consists of hardware design engineers, embedded software engineers, and hardware/software co-design architects. Engineers can understand other technical domains and get a chance to learn how to work with engineers in other technical domains. Architects can learn co-design skills and try them in a team.

This class is originally developed by QUBE. We describe detail of this class and its material in section 4.

## (2) Advanced Design Technology Program

Advanced Design Technology Program aims at educating deeply professional design technology in each technical domain. In this program, QUBE also provides System LSI related management classes. Classes in this program are provided by professors engaged in System LSI related advanced research and development. These professors are invited from Kyushu University, other universities, and industry. In this program,

This program consists of four courses:

## 1) Hardware design technology course

This course provides hot topics related to hardware design technologies for System LSI such as noise, power/signal integrity, RF, large-scaled design, *etc*.

## 2) Embedded software design technology course

This course provides topics about development methodologies, test, RTOS, and middleware for software embedded into System LSI.

## 3) Hardware / software (HW/SW) co-design technology course

This course provides topics for co-design technologies such as development methodology using ASIP, C-based design and low-power design for System LSI.

#### 4) Technology management knowledge course

This course provides topics for managing System LSI projects such as intellectual properties and management of technology.

We make session time of classes in this program short and provide multiple classes in one year to ease taking classes for engineers who have business. Session time of classes are between one day and a week.

## 6. SYSTEM LSI DESIGN TRAINING CLASS

This section explains the System LSI Design Training Class.

## 6.1 Lecture Plan

This class consists of four parts; lecture, tutorial, exercise (analysis, design, implementation), and presentation. QUBE plans to maximize exercise time to make this course practical. QUBE provides tutorials to make students familiar with the target board and development environment like [6].

## AM of 1st, 2nd day: The Lecture

At AM of 1<sup>st</sup> and 2<sup>nd</sup> day, QUBE lectures knowledge to design and implement System LSI as follows:

- 1) About System LSI

- 2) Viewpoint of System Design

- 3) Basics of Hardware Design

- 4) Basics of Software Design and Implementation

- 5) Cost model of System LSI

- 6) Low Power Design for System LSI

## 7) HW / SW Co-Design

## PM of 1st, 2nd day: Tutorial

At PM of 1<sup>st</sup>, 2<sup>nd</sup> day, QUBE provides tutorials to make students familiar with development environment and to learn skills to develop System LSI.

Professors lecture to use development environment step by step. Professors incrementally give students exercises to connect a processor and original hardware both of designing hardware and developing device drivers as follows:

- 1) Write a device driver for given LED controller

- 2) Design a original LED controller

- Design a push button switch controller and Write device driver for it

## 3<sup>rd</sup>, 4<sup>th</sup> day: Analysis / Design

At first of the 3<sup>rd</sup> day, professors explain the exercise target. Students analyze and design it and make documents at the 3<sup>rd</sup> and 4<sup>th</sup> day.

## $4^{th} - 7^{th}$ day: Implementation / Verification / Test

At the 4<sup>th</sup> to 7<sup>th</sup> day, students design hardware and/or implement embedded software. Hardware and software components such as OS, middleware, *etc.*, are provided in order to decrease developing time. Students develop an exercise target using these components.

## 8th day: Presentation

At the last day, each team gives presentations including the results of analysis and design. They also demonstrate a system implemented by them. Professors request a peer review to their documents. Students discuss about their design based on their documents.

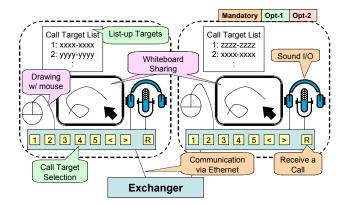

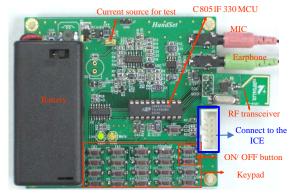

#### **6.2 Multimedia Phone**

QUBE select Multimedia Phone (MMP), which is a multi functional phone, as exercise target. Overview of MMP is shown as Figure 2. MMP has call / hook function, voice communication function, MMP discovery function, and white board sharing function. MMP equips microphone and speaker for voice communication. MMP also equips a LCD and a mouse for white board sharing. There are multiple MMPs in a network, and MMPs are connected via Ethernet.

To make exercise target scalable, QUBE provide two function profiles: basic profile and extended profile. First, students implement MMP according to the basic profile. If exercise time remains, they extend it according to the extended profile. Thus, the exercise target can be applicable to students who have various

Figure 3 Overview of the Multi Media Phone

skill levels.

For the exercise environment, in which students can implement MMP, QUBE provides Xilinx XUP Virtex II Pro board and its development environment. The board equips a FPGA (Virtex II Pro) embedded two PowerPC 405 processors, an ethernet interface, an audio codec based on AC97, two serial interfaces, some buttons, a VGA interface, a keyboard interface, and a PS/2 mouse interface. QUBE employs ISE and EDK as a development environment. QUBE also provides some debug tools such as Ethereal which is a packet capturing tools, WinPcap which is a library to develop software dealing with ethernet frame, and MMP emulator executed on PCs.

## 6.3 1st run Report

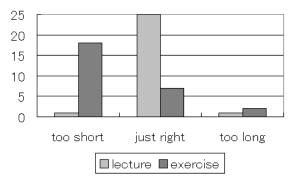

This subsection reports briefly the 1<sup>st</sup> run of System LSI Design Training Class at March 1 to 10, 2006. Five applicants from industries and two applicants from a university subscribed to this course. QUBE made two teams from them.

Basically, professors lectured according to the plan mentioned in section 5.1. QUBE also provide short lectures in which professor lecture basic topics requested by students who want to know such topics. In this time, mechanism of interrupt, OS, and drivers are requested. The students want the short lecture due to engineers are not educated enough about basic topics at fields in industries in Japan.

After lectures, each team designed and implemented the MMP respectively. Development speed was slower than supposed one at course designing phase.

Finally, each team gave the presentation of the design of MMP and demonstrated their MMP. They designed and wrote

| Table 1 Statistics of the | ne applicants |

|---------------------------|---------------|

|---------------------------|---------------|

|                | orga | nizations | registered |         | total applicants |       |           |          |    |      | Diploma |     | taken<br>classes | pass  |

|----------------|------|-----------|------------|---------|------------------|-------|-----------|----------|----|------|---------|-----|------------------|-------|

|                |      |           |            |         | appli            | cants | cancelled | absenced | pa | ssed | F       |     | /a student       | ratio |

| Total          | 40   |           | 106        |         | 149              |       | 15        | 2        | 98 |      | 20      |     | 1.25             | 74%   |

| Non students   | 37   | 93%       | 87         | 82<br>% | 124              | 83%   | 14        | 2        | 89 | 91%  | 20      |     | 1.24             | 82%   |

| Industries     | 32   | 80%       | 76         | 72<br>% | 101              | 68%   | 12        | 2        | 76 | 78%  | 16      | 80% | 1.14             | 87%   |

| Non industries | 5    | 13%       | 11         | 10<br>% | 23               | 15%   | 2         | 0        | 13 | 13%  | 4       | 20% | 1.91             | 62%   |

| Students       | 3    | 8%        | 19         | 18<br>% | 25               | 17%   | 1         | 0        | 9  | 9%   |         |     | 1.26             | 38%   |

documents satisfactorily. The team of students from industries designed according to eUML[7], which is a development methodology for embedded system based on UML. Another team designed according to PLUS[8], which is a one of the product lines development methodology. Each team implemented the MMP based on basic profile only. They could not implement functions as hardware logics.

To run this 1<sup>st</sup> class, QUBE developed course materials such as lecture slides, software and hardware components for learning knowledge and know-how to lead projects in which engineers should design both of hardware and software.

QUBE found a problem through running this 1<sup>st</sup> class that the exercise time is too short to implement functions using both of hardware logics and software. The reason is that skill levels of students are lower than supposed one. QUBE has a plan to extend exercise target to cover students who are in entry level.

## 7. PROJECT ACTIVITIES in 2005

In this section, we report results of QUBE classes run in 2005. Its statistics are shown as Table 1.

We provided 16 classes (35 days) in 18 weeks according to the plan. 106 applicants ware registered to QUBE classes. Most of registered applicants ware belong to Fukuoka area as same prefecture as QUBE. Total 132 applicants took these classes and the average applicants in each class are 8.3.

98 students passed these classes. We supposed the pass ratio is over 90% at designing the QUBE curriculum. But real pass ratio was 74%. Its reason is that levels of each class ware higher than students' skills. The pass condition is that taken point is over or equal 70 points. The points consist of 40 attendance points, 10 report submission points, and 50 lecturer points.

Diploma students are 20, through the set points of diploma students are 360 in 5 years. These reasons are numbers of students is less than supposed one and the supposed pass ratio is too high as mentioned. The diploma condition is that a student should pass one class in System LSI Designer Education Program or two classes in Advanced Design Technology Program.

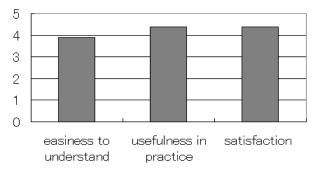

QUBE requested writing questionnaires to the students. The result

of the questionnaires is as shown in Table 2. Most of the motivation to take QUBE class was applicants' wish for learning knowledge and skills supposed to use in near feature. Engineers in fields in industries have motivation to learn new knowledge and skills themselves. Satisfaction for their prospect is 74%, which is sum of percentage of very good and good. Their feelings of the levels of the classes, however, are distributed by class. Total points of their satisfaction are 89%, which is sum of percents of very good and good.

QUBE can provide classes satisfied by students according to this questionnaire. However, QUBE should tackles to improve pass ratio. One of the cause of such low pass ratio is applicants don't know required skill level to understand classes enough. QUBE have a plan to improve it to clarify target skill level that applicant can understand lectures and to clarify the goal skill level that applicants can understand to take lectures according to the Embedded Technology Skill Standard[9]. QUBE also tackles to adjust levels of classes to applicants needs. QUBE also make publicity to industries in Kyushu area to increase applicants.

#### 8. CONCLUSIONS

This paper introduced the Education Program for System LSI Designers referred to as QUBE. QUBE aims at educating system LSI designers who have wide knowledge and practical skills both of hardware and embedded software.

QUBE made a curriculum that students can learn advanced hot topics in each technical region and exercise to design and implement System LSI which consists of hardware and embedded software. QUBE originally developed an exercise centric course material for latter program in the curriculum. QUBE provides 16 classes (35 days) in 18 weeks according to the plan in 2005 school year. 106 applicants ware submitted to classes. 89% students ware satisfied with QUBE classes according to questionnaire.

In the feature, QUBE will improve course materials constantly to adapt new technologies. QUBE also will tackle to improve pass ratio adjusting a level of classes to applicants needs. QUBE make publicity to industries in Kyushu area to increase applicants.

Table 2 The result of questionnaire to the students

| 1. Motivations          | 1.1 What                                         | a) As an induction course                          |                | <u>7</u>  | <u>6%</u>  | 2. Remarks               | 2.3-1 How did you                 | a) Very good         |    | 26% |

|-------------------------|--------------------------------------------------|----------------------------------------------------|----------------|-----------|------------|--------------------------|-----------------------------------|----------------------|----|-----|

|                         | occasion did<br>you take this                    | b) Advice from                                     | n your boss    | <u>24</u> | 22%        | to the class<br>(cont'd) | understand topics in the lecture? | b) Good              | 38 | 35% |

|                         | class.                                           | c) Your wish                                       |                | <u>75</u> | <u>69%</u> | (cont a)                 |                                   | c) Average           | 32 | 29% |

|                         |                                                  | d) Others                                          |                | <u>4</u>  | <u>4%</u>  |                          |                                   | d) Bad               | 11 | 10% |

|                         | 1.2 Why did                                      | a) for current bussiness                           |                | <u>36</u> | 33%        |                          |                                   | e) Very bad          | 0  | 0%  |

|                         | you take this class?                             | b) for business in near feature                    |                | <u>45</u> | <u>41%</u> |                          | 2.5 How did you                   | Describe good points | 67 | 61% |

|                         | <u>class?</u>                                    | c) not for your                                    | r business     | <u>31</u> | <u>28%</u> |                          | feel about the text?              | Describe bad points  | 47 | 43% |

|                         |                                                  | d) Others                                          |                | <u>7</u>  | <u>6%</u>  |                          | 2.6 What did you                  | Describe good points | 66 | 61% |

| 2. Remarks to the class |                                                  | 2.1-2 How was you satisfied with your prospect? a) |                | <u>37</u> | 34%        |                          | find something while the lecture? | Describe bad points  | 40 | 37% |

|                         |                                                  |                                                    | <u>b) Good</u> | <u>48</u> | 44%        |                          | 2.7-1 Time of the lecture         | b) not appropreately | 12 | 11% |

|                         |                                                  |                                                    | c) Average     | <u>19</u> | <u>17%</u> |                          | 2.8 Total point                   | a) Very good         | 47 | 43% |

|                         |                                                  |                                                    | <u>d) Bad</u>  | <u>5</u>  | <u>5%</u>  |                          |                                   | b) Good              | 50 | 46% |

|                         |                                                  |                                                    | e) Very bad    | 0         | 0%         |                          |                                   | c) Average           | 12 | 11% |

|                         | 2.2 How did you feel about level of the lecture? |                                                    | <u>a) Easy</u> | <u>57</u> | <u>52%</u> |                          |                                   | d) Bad               | 0  | 0%  |

|                         |                                                  |                                                    | b) Difficult   | <u>52</u> | <u>48%</u> |                          |                                   | e) Very bad          | 0  | 0%  |

## REFERENCES

- [1] Yasuura, H., Tsukizoe, A., Hirakawa, K., Ito, N., and Nakano, S., "College of System LSI, Fukuoka: A Callenge to Sillicon Sea Belt (in japanese)", Journal of IEICE, Vol.86, No.11, pp.857-863, 2003.

- [2] Huang, T., King, C., Lin, S. Y., and Hwang, Y.,: The Embedded Software Consortium of Taiwan, ACM Transactions on Embedded Computing Systems, Volume 4, Issue 3, pp. 612 – 632, 2005.

- [3] Yamamoto, M., Tomiyama, H., Takada, H., Agusa, K., Masa, K., Kawaguchi, N., Honda, S., Kaneko, N.: NEXCESS: Nagoya University Extension Courses for Embedded Software Specialists, Proc. 2005 Workshop on Embedded System Education (WESE2005), pp.16-20, 2005.

- [4] VLSI Design and Education Center: About VDEC, http://www.vdec.u-tokyo.ac.jp/English/index.html.

- [5] Institute of System LSI Design Industry, Fukuoka: The design and verification lab (in Japanese), <a href="http://www.ist.or.jp/lsi/">http://www.ist.or.jp/lsi/</a>.

- [6] Edwards, S. A.: Experiences Teaching an FPGA-based Embedded System Class, Proc. 2005 Workshop on Embedded Systems Education (WESE2005), 2005.

- [7] Watanabe, H., *et al*: Embedded UML: Object Oriented Development Using eUML(in Japanese), Syoueisya, 2002.

- [8] Gomma, H.: Designing Software Product Lines with UML: From Use Cases to Pattern-Based Software Architectures, Addison-Wesley, 2004

- [9] IPA, Japan: Embedded Technology Skill Standard (ETSS), <a href="http://sec.ipa.go.jp/std/skillex\_eb.php">http://sec.ipa.go.jp/std/skillex\_eb.php</a> (in Japanese).

## The Embedded Software Consortium of Taiwan - A Progress Report of Educational Activities

Tai-Yi Huang and Chung-Ta King Department of Computer Science National Tsing Hua University {tyhuang, king}@cs.nthu.edu.tw

Shih-Hao Hung

Department of Computer Science and Information Engineering

National Taiwan University

{hungsh}@csie.ntu.edu.tw

## Abstract

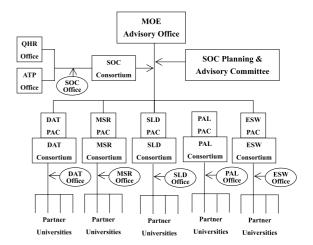

To meet the challenges brought by recent advancement on semiconductor manufacturing technology to develop system-on-chip (SoC) techniques, the Ministry of Education (MOE) of Taiwan has been running the VLSI Circuits and Systems Education Program since 1996. This program is currently at its third phase of revision, which starts at 2006 and ends at 2010. The Embedded Software (ESW) Consortium is one of the 8 domain-specific, inter-collegiate consortia funded by the MOE under this program. The goal of ESW is to address the challenges of embedded software development for SoC systems. This paper first introduces the VLSI Circuits and Systems Education Program. The organization and activities of ESW is described next. Finally, we present an execution summary of ESW in the past three years.

**Keywords:** embedded software, integrated circuit design, educational programs

## 1 Introduction

The continuous advancement in nanometer semiconductor manufacturing, integrated circuit (IC) design, and system-on-chip (SoC) techniques has made practical to place on a single chip a complete computing system. The key to the success in the development of a SoC industry depends on a large number of well-educated engineers on IC design, embedded software, and system integration, in addition to supporting personnel in business, management, and law. The Ministry of Education (MOE) of Taiwan has

been running the VLSI Circuits and Systems Education (CSE) Program since 1996. The program is to provide our local semiconductor industry with its needed technology and engineers, both in quality and quantity. Phase I of this program began in 1996 and ended at 2000. The objective of this phase was primarily to establish fundamental IC design environments at universities in Taiwan to promote IC design research and new educational curricula. Phase II of this program continued at 2001 and ended at 2005. To make its decision process and execution efficiently, Phase II adopted a top-down approach by forming six domain-specific, inter-collegiate consortia. This consortium architecture is further expanded into eight consortia in Phase III that begins at 2006 and will end at 2010.

The ESW Consortium, established in February 2004, is the latest consortium founded by the MOE under the VLSI CSE Program to address the challenges of embedded software development for SoC systems. A SoC system, different from a traditional board-level system, places on a single chip all system components, including one or more microprocessors, cache, memory, and communication modules. Traditional board-level system software cannot fully utilize the resources of a SoC system if directly ported. In addition, these software are often developed to support a wide variety of platforms. In contrast, a SoC system software is mostly designed for a specific platform. The ESW Consortium intends to achieve its goal by integrating resources from the government of Taiwan, domestic and foreign academic societies, and local semiconductor industry. The programs of ESW include academic and industrial forums, international

collaborations, student activities and promotion, and a new embedded software curriculum.

The VLSI CSE program of Taiwan and the ESW Consortium was formally introduced in [1]. We described the Phase II of the CSE program, the supplydemand analysis of the local semiconductor industry, the six-consortia architecture, and an execution summary of ESW in 2004. In this paper, we update the recent progress of the CSE program and the ESW Consortium. We first briefly describe the Phase III program and the eight-consortia architecture. We next provide an ESW execution summary in 2006. The execution report focuses on the 2006 Embedded Software Design Contest (ESDC) and the ESW hands-on lab map. The ESDC, hosted by the MOE of Taiwan, is an annual event in which students compete with their constructed embedded systems in both creativity and advanced technology. This event has been used by ESW to evaluate and demonstrate the performance of their reformed ESW curriculum. A number of hands-on labs are produced during the development of the ESW curriculum. We started a new project in 2005 to classify and integrate all these labs into a comprehensive map of labs. This map serves both as a handbook for professors to select labs suitable to their courses and as a guide for ESW to advance its curriculum. Finally, due to the space limit, we skip the update on the ESW curriculum that includes more courses than its shape in 2004.

The rest of the paper is structured as follows. Section 2 introduces the Phase III of the CSE program. Section 3 presents the latest results of ESDC. Section 4 describes our efforts in constructing a comprehensive map of hands-on labs. An execution summary of other ESW activities is reported in Section 5. Finally, Section 6 concludes this paper.

## 2 The VLSI CSE Program

The VLSI CSE program was initiated in 1996 by a group of senior professors and industry leaders who envisioned that high-quality IC design engineers will be essential to its local semiconductor industry. The execution of the VLSI CSE program can be divided into three phases. The Phase I executed from July 1996 to December 2000. Its primary goal was to establish advanced VLSI design curricula in around 20 research-oriented universities. The Phase II executed from January 2001 to December 2005. Recognizing that SoC is a must-have technology, Phase II took an aggressive top-down approach to form a six-consortia architecture. A top-level office named the SOC Consortium [6] hosts all cross-consortia activities while

Figure 1: The eight-consortium architecture

each sub-level consortium manages its own domain-specific events. Along with the execution of the CSE program, the MOE founded the Chip Implementation Center [3] that offers its service of manufacturing chips designed by students. Total funding for Phase I and Phase II are US\$3M and US\$15M, respectively. In addition, there are around 1,000 chips fabricated and tested by the CIC each year.

Phase III starts at January 2006 and will end at December 2010. Its purposes are two folds: to continue what we have achieved and to make our results visible to international communities. To adapt to its fast growth in scope and impact, Phase III expands its consortium architecture to an eight-consortia one, as shown in Figure 1. There are four levels of administrations. The advisory office of the MOE defines general guidelines and approves budget planning. The SOC Consortium coordinates and monitors activities among all consortia. The DAT (Design Automation & Testing), MSR (Mixed Signal & Radio Frequency), SLD (System-Level Design), PAL (Prototyping Application & Layout), and ESW (Embedded Software) are domain-specific consortia, each of which has a group of partner universities to define its curriculum and activities. Both the QHR (Quality Human Resources) and ATP (Advanced Teaching Platform) consortia are added in Phase III to coordinate cross-consortia activities. QHR hosts all programming contests, invites international speakers, and sponsors cross-consortia activities. These contests are the IC Design Contest, the Silicon IP Authoring Contest, the EDA Programming Contest, and the Embedded Software Design Contest. Each contest is held annually to provide a platform for student competition and performance evaluation. ATP promotes new curricula developed in all consortia by providing the financial support needed to adopt a new curriculum. The total funding for Phase III is increased to US\$20M proximately.

The organization of the ESW Consortium remains much the same as we reported in [1]. The ESW office is currently based at National Tsing Hua University and chaired by Professor Chung-Ta King. Professor Tai-Yi Huang serves as the executive secretary since ESW was first founded in February 2004. Its planning and execution is supervised by an independent Planning and Advisory Committee (PAC) consisting of one senior researcher and four industry leaders. Its programs are classified into five main categories: embedded software forums, student activities and promotion, international cooperation programs, industrial strategic forums, and the embedded software curriculum. There are totally 22 partner universities of which 46 professors are involved in planning and executing ESW activities. All information and promotions are published and accessible at its official web site [5].

# 3 The Embedded Software Design Contest

The annual ESDC event is sponsored by the MOE and organized by the QHR Consortium. The first ESDC was held in 2003 for the purpose of demonstrating the capability of embedded software design and development. Since 2006, ESDC is organized by Professors Tei-Wei Kuo and Shih-Hao Hung at National Taiwan University. A full ESDC schedule spans over four months. Each team can have no more than three students, with no restriction on undergraduate and graduate students. Each team registers by submitting a proposal describing its project scope and working list. Each proposal is reviewed by the program committee to provide early feedback and suggestions. There is a period of two months for students to complete their working list. A final report is due two weeks prior to the final on-site demonstration. The score of a project is based on its final report (30%), its oral presentation (20%), and the system demonstration (50%). We evaluate a project by its software originality and creativity, soundness of software engineering, and system performance, depending on which category of competition it is registered for. A winning team is financed as an award to attend one international conference related to embedded system and software.

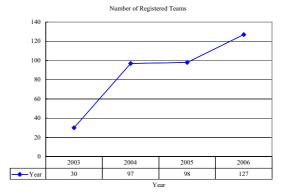

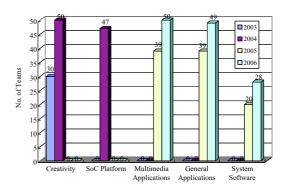

Figure 2 shows the total number of registered teams from 2003 to 2006. There were only 30 teams

Figure 2: The number of registered teams

Figure 3: The number of teams in each category

in 2003 when ESDC first took place. This number increases significantly to 97 in 2004 when the ESW Consortium was founded. As the ESW curriculum continues to develop and be deployed in more universities and colleges of technology, this number reaches a record-high of 127 in 2006.

In 2003, there is only one contest category of Creativity. In 2004, ESDC added a new category of SoC Platforms to attract more hardware-centric students. Each team is allowed to register only in one category. Figure 3 shows the number of registered teams in each category. A team registered for Creativity has an open choice of embedded platforms, and their work was evaluated on its software originality and creativity. A team registered for SoC Platforms can only work on a list of designated platforms and was evaluated on its software efforts in design tradeoffs and resource optimizations. Starting in 2005, we made ESDC as a thee-category contest based on areas of applications. The category of Multimedia Applications is there in response to the ever-growing inter-

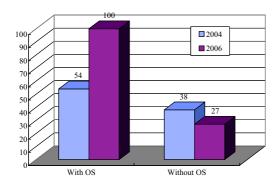

Figure 4: The types of embedded systems

Figure 5: Classification by operating systems

ests and ideas in multimedia. The category of General Applications provides the arena for students to showcase their creativeness and skills without limit of topics and platforms. Finally, the category of System Software is designed to encourage the research and development efforts in embedded system software such as the operating systems, middleware, compilers, and device drivers.

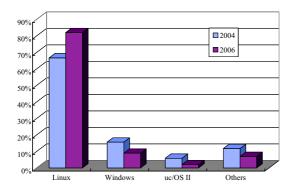

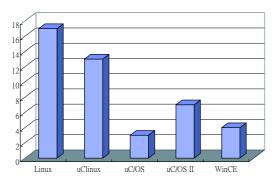

Figure 4 shows the number of projects that are managed by an operating system or by a mere loop scheduler in 2004 and 2006. It is an interesting observation that more students choose to work with an operating system to implement complex applications, manage real-time tasks, and handle sophisticated embedded platforms. It is also an indication of stronger competition and more advanced skills of participated students from 2004 to 2006. Furthermore, Figure 5 breaks down the types of operating systems adopted by students. In 2006, 82% of participated teams chose Linux, higher than the 67% adoption in 2004. This shows the dominance of Linux in our academic society of embedded software. This dominance results from the flexibility and availability of Linux-based de-

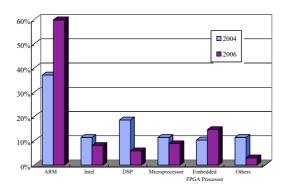

Figure 6: Classification by processors

Figure 7: Classification by topics

velopment kits and strong educational and industrial support behind Linux.

Figure 6 shows the classification by processors. The percentage of ARM-based processors increases from 37% in 2004 to 60% in 2006, well demonstrating the dominance of ARM-based processors in the local market. There are more network and multimedia applications developed with FPGA prototyping in 2006 while there are less projects utilizing DSP processors. If we classify projects by user-mode and kernel-mode, about 80% of projects are user-mode applications while 20% of them are kernel-based modules including operating systems, device drivers, and system-related tools. We noticed this distribution since 2004 and have made a strong effort to encourage and promote the development of kernel-level software. In fact, the category of System Software is created to address this need. The improvement of technology and skills demonstrated by projects in this category is considered superior to what we observed in the other two categories.

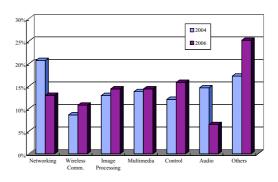

Figure 7 further classifies user-mode projects by domains of applications. Generally speaking, net-

| Year | Category                | Project Topics                                                      |

|------|-------------------------|---------------------------------------------------------------------|

|      | Multimedia Applications | An integrated design of OSGi gateway and DVB interactive platform   |

|      |                         | An intelligent digital camera with adjustable power and performance |

| 2005 | General Applications    | e-Housekeeper                                                       |

|      |                         | Realization of human-robot interaction via vision capturing         |

|      | System Software         | Software-less SCAN sensor                                           |

|      |                         | A memory protection mechanism in an embedded OS                     |

|      | Multimedia Applications | An intelligent guide for emergency fire exit                        |

|      |                         | Embedded H.264 video streams                                        |

| 2006 | General Applications    | 3G entertainment - Good, Great, General                             |

|      | System Software         | A low-power real-time operating system                              |

|      |                         | A fast multi-core simulation framework with synchronization IP      |

Table 1: The topics of winners in each contest category

working (including wired and wireless) applications and multimedia (including audio and image processing) applications are favored. The category of Others includes projects in the domain of security, health, and kernel-level topics. Finally, Table 1 lists the winners in each contest category of 2005 and 2006. Most winners of 2003 and 2004, available in [1], use multimedia applications to demonstrate their embedded software. On the other hand, many winners in 2005 and 2006 developed embedded systems that efficiently integrate system resources of hardware and software. The latter winner certainly requires more understanding and training on embedded software. This trend is again considered as an indication to the success of the ESW curriculum.

In summary, after four years of strong competition, our experience from ESDC confirms that this government-sponsored annual event has become a great force in promoting embedded software research and educational programs. In addition, it also helps to reveal the strength and weakness in our ESW curriculum. The program committee of ESDC continues to observe increased quality and complexity in the proposed projects. An active item of future work is to encourage more kernel-level embedded software and increase the number of teams in System Software.

## 4 The Hands-on Lab Map

The development of the ESW curriculum is to provide a set of lab-centric courses. Each course was first designed by a group of four professors and was later adopted by interested universities. An adoption of a course receives financial support by the MOE to setup a lab for its purpose. In return, each adoption is required to provide at least 4 sets of hands-on labs at its final review. The ESW office has collected 80 labs from 8 different courses. We label each lab with an

index of *CourseNum-UnivNum-LabNum*. For example, a lab module with a label of 002-01-03 indicates that it is the third lab module developed by the first university for the second course.

For ease of reference, we classify these 80 modules by three categories: platforms, operating systems, and tool chains. There are currently 14 embedded platforms and 5 different operating systems. Due to the space limit, we only give out partial information of each classification table in the following. The complete tables are accessible at the official web site of ESW [5].

## 4.1 Classification by Platforms

Table 2 gives part of our classification by platforms. The first column lists the platforms used in each set of labs. The second column lists the operating system used by these labs. An empty slot of this column indicates that no operating system is installed. In contrast, if an operating system is ported as a lab, we provide its label for reference. The third column gives the topic of this lab and the fourth column gives its label. This table helps ESW professors to easily identify the platform suitable to their teaching needs. In addition, it serves as a map to develop unavailable modules for a selected platform, avoiding redundant efforts.

## 4.2 Classification by OS

There are 5 different operating systems used among all lab modules. Figure 8 shows the name of these operating systems and the number of labs installed with each operating system. Linux-based operating systems are strongly favored by these hands-on labs. Table 3 gives part of our classification by operating systems. The first column shows the name of the

| Platform        | OS                | Topic                               | Label       |

|-----------------|-------------------|-------------------------------------|-------------|

|                 |                   | LCD Display                         | [001-02-01] |

| Creator S3C2410 | Linux 2.4         | MP3 Player                          | [001-02-03] |

|                 | [001-02-02]       | RT-OS module FireLinux              | [001-02-04] |

|                 |                   | Bootloader                          | [001-03-03] |

|                 | uClinux 2.0       | Switch and 7-segment                | [001-03-05] |

| NET-Start!W3001 | [001-03-04]       | Interrupt Handlers and Time Delay   | [001-03-06] |

| ARM S3C4510B    |                   | DMA                                 | [001-03-07] |

|                 | uC/OS [001-03-08] | Scheduler: Priority-inversion Issue | [001-03-09] |

Table 2: The classification of labs by platforms

| OS      | Platform        | Topic                             | Label       |

|---------|-----------------|-----------------------------------|-------------|

|         |                 | Porting Linux 2.4                 | [001-02-02] |

|         | Creator S3C2410 | MP3 Player                        | [001-02-03] |

|         |                 | RT-OS Module FireLinux            | [001-02-04] |

|         |                 | Porting Linux 2.4                 | [001-04-01] |

| Linux   |                 | IPC (Share Memory & Semaphore)    | [001-04-01] |

|         | TI OMAP 5910    | PThread Programming               | [001-04-01] |

|         |                 | Embedded GUI Programming          | [001-04-01] |

|         |                 | Networked Digital Camera          | [001-04-01] |

|         |                 | Poring uClinux 2.0                | [001-03-04] |

|         |                 | Bootloader                        | [001-03-03] |

| uClinux | NET-Start!W3001 | Switch and 7-segment              | [001-03-05] |

|         | ARM S3C4510B    | Interrupt Handlers and Time Delay | [001-03-06] |

|         |                 | DMA                               | [001-03-07] |

Table 3: The classification of labs by operating systems

4.3

Figure 8: The number of labs with each OS

| Topic                  | Label       |

|------------------------|-------------|

|                        | [001-03-01] |

| ARM Development Suite  | [001-03-02] |

|                        | [001-07]    |

|                        | [001-08]    |

| ARM SDT                | [001-05]    |

| Hitool                 | [001-10-02] |

|                        | [003-01-01] |

| ARM GCC Cross-compiler | [002-01-01] |

|                        | [003-01-01] |

Table 4: The classification by tool chains

Classification by Tool Chains

# operating system and the second column shows the platform. The third and the fourth columns show the topic of a lab and its label. By this table, an interested professor can easily find out the topics of labs and platforms for her favored operating system. Similarly, a new course on embedded operating systems or related topics can enhance this table by developing

unavailable lab modules.

One major category of courses in the ESW curriculum is to develop tool chains for embedded platforms. These tool chains are mainly compilers and debuggers. There are totally 16 labs related to the development of tool chains. We classify these labs by its developed tool. Table 4 gives partial information about this classification.

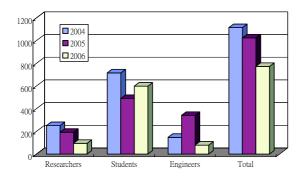

Figure 9: The attendance summary report

Figure 10: The attendance report by events

## 5 Execution Summary

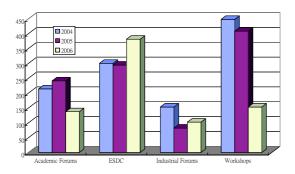

Figure 9 shows the attendance report of ESW activities in the past three years. There are totally 1115, 1025, and 773 persons in 2004, 2005, and 2006, respectively. We further break down this number by two different categories. Figure 9 also lists the attendance by roles: academic researchers, students, and industrial engineers. On the other hand, Figure 10 breaks down this number by events: academic forums, ESDC, industrial forums, short courses or workshops. In the following, we analyze this data by events and show some interesting observations. Our comparison mainly focuses between 2004 and 2005. Because the calendar of 2006 is still in its early July dates, no direct comparison will be made.

## 5.1 Academic Forums

We held four academic forms in both 2004 and 2005. The number of academic forums will be reduced to 3 in 2006 and each forum will have a limit of 40 persons to foster more focused discussions. The attendance increases from 214 in 2004 to 241 in 2005. There are two reasons behind this increase. First, we were only

exploring topics when ESW was first founded in 2004. When entering 2005, we had better ideas about what will interest academic researchers. The selection of topics is therefore more customer-oriented. The topics of the forums in 2005 are "Quality of Services and Care for the Elderly", "Building Structurally Stable Embedded Software", "Compilers and Software Development Toolchains for Embedded Systems", and "The Promotion of Embedded Software Research and Education in Taiwan". The other reason of having a better attendance is to co-locate a forum with a short course or a workshop. This strategy proves to be successful for both forums and workshops since an interested audience can attend two events in one trip.

## 5.2 International Programs

In 2004, we executed the international cooperation program by inviting renowned international scholars to Taiwan to give a short course or a tutorial and exchange research ideas with local researchers. In 2005, we added one more item by sponsoring researchers to attend foreign events such as an international conference or an education program held by an academic institute or a company. We extend this vision in 2006 to actively participate in international activities of embedded software research or education. In fact, this submission, along with other submissions of ESW, to this workshop is part of this effort. At the invitation of international scholars, we invited Professor Lui Sha [4] from the University of Illinois at Urbana-Champaign to talk about the construction of reliable and stable embedded software in September 2005. We also invited Dr. Stephen Kent [2] from BBN Technologies to give a short course about the issues, practices, challenges, and opportunities of VoIP security in July 2006.

## 5.3 Industrial Forums

The industrial forums of 2004 addressed on subjects that interest both academic researchers and industrial engineers. Starting in 2005, we executed industrial forums to discuss more industrial-focused subjects. As a result, less researchers attended these forums while more engineers were attracted to participate. We considered it a positive change and continue to execute likely in 2006. The forums of 2005 featured two panel discussions, one on the subject of providing the embedded software engineers needed by industry and another one on the subject of constructing profit-oriented business models. We held one industrial forum so far in 2006. This forum featured a panel discussion of research and development

of turn-key technology in embedded software.

## 5.4 Short Courses and Workshops

To promote ESW events and attract more audience, we co-located academic forums with a short course in 2005. This short course presents a 6-hour content describing the bootstrapping process of Linux, the O(1) scheduler introduced in 2.6, and a couple of hands-on lab to construct a multi-tasking embedded operating system. This short course was held three times, each of which drew more than 100 students and engineers to attend. The success of this short course and its high attendance encourages us to bring together multiple events of similar audience in 2006. In addition, we also held one workshop during the period of ESDC to provide the training required for platform adoption as well as share some successful stories from previous ESDC winners.

The ESW curriculum now consists of 12 courses, 9 of which completed its design in 2005 and another 3 of which were newly added in 2006. The courses that are completed by 2005 have been adopted by 11 universities already. To introduce and promote these courses, we hold at least 2 workshops each year to briefly go over the content and structure of each course. These workshops also provide a platform for interested professors to exchange their teaching experience. In 2006, we further expand this effort to have an overview workshop of all courses and a labcentric workshop for each course. All these workshops are planned and will be held in August 2006. Finally, the ESW curriculum for technical colleges is currently under development. It is expected to be ready for adoption by September 2006.

## 6 Conclusions

The MOE of Taiwan has been running this VLSI CSE program since 1996, in order to provide well-trained students both in quality and quantity for its local semiconductor industry. Over the past 10 years, the previous two phases of the CSE program have successfully achieved its educational goal. This program has made Taiwan stayed in a leading role in many sectors of the semiconductor industry. The ESW Consortium, the last consortium founded by the MOE during Phase II, is to address challenges and opportunities in embedded software for SoC systems. Starting 2006, the CSE program enters its third phase of revision. The importance of cultivating talents for embedded software is commonly recognized by senior researchers and industrial leaders in a number of

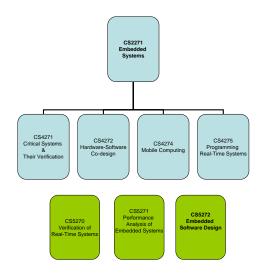

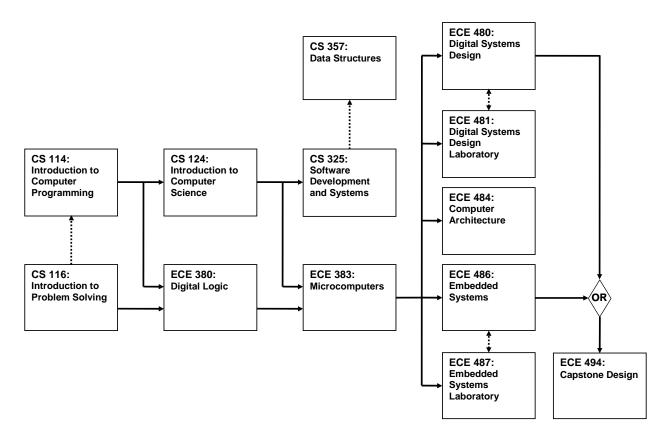

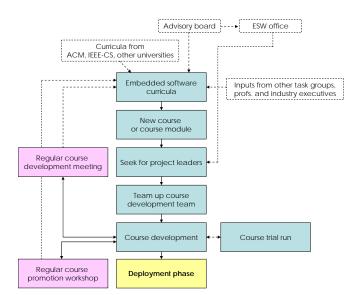

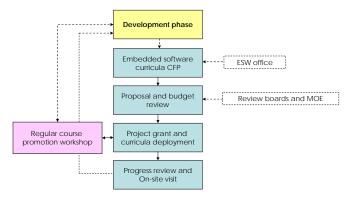

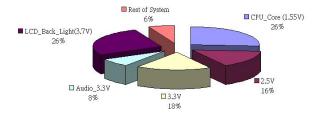

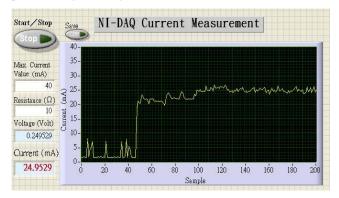

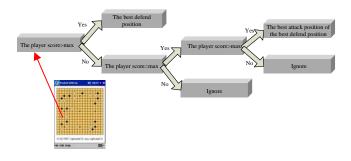

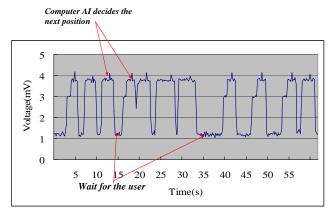

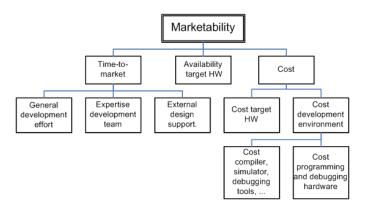

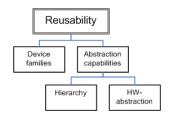

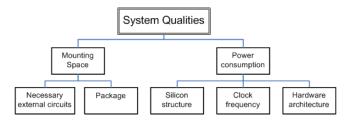

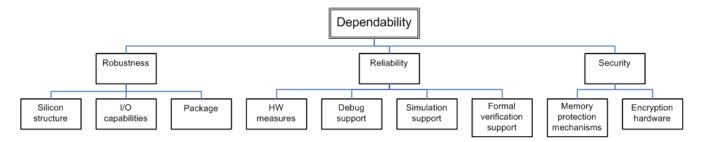

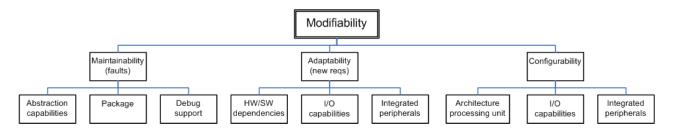

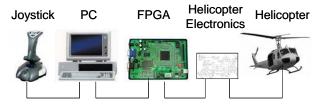

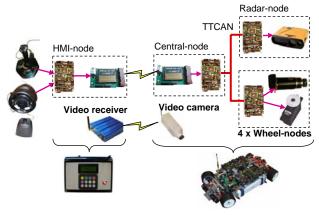

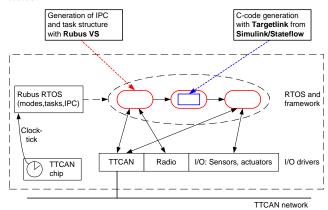

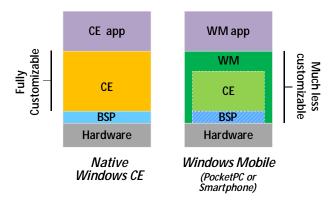

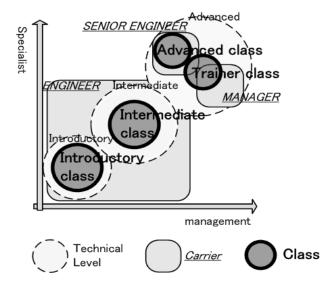

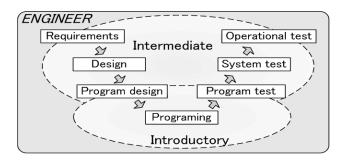

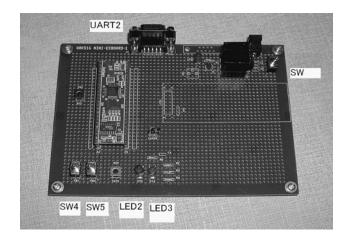

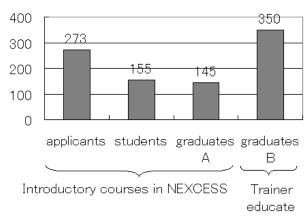

meetings. Accordingly, more resources will be placed on the ESW Consortium during Phase III.